DX-MRAM based

HBM : High-Capacity Potential

HBM : High-Capacity Potential

DX-MRAM

Chip : High-Capacity Potential

|

< 10nm

Process Node Enabling smaller, more efficient chips < 10nm

Process Node Enabling smaller, more efficient chips |

DX-MRAM

Cell : High-Density Potential

Cell : High-Density Potential

|

~ 12x

Density Increase

Compared to SRAM cell |

The 12x higher density of DX-MRAM cells compared to SRAM cells offers significant advantages for neuromorphic semiconductor applications in several innovative ways:

1. High-Density Synaptic Array Implementation: 2. Reduced Chip Area and Power Consumption: 3. Enhanced On-Chip Learning Capabilities: 4. Potential for Novel Neuromorphic Computing Paradigms: In conclusion, the 12x higher density of DX-MRAM cells has the potential to significantly improve the performance, power efficiency, and integration density of neuromorphic semiconductors, paving the way for new AI applications and advancements in the field. |

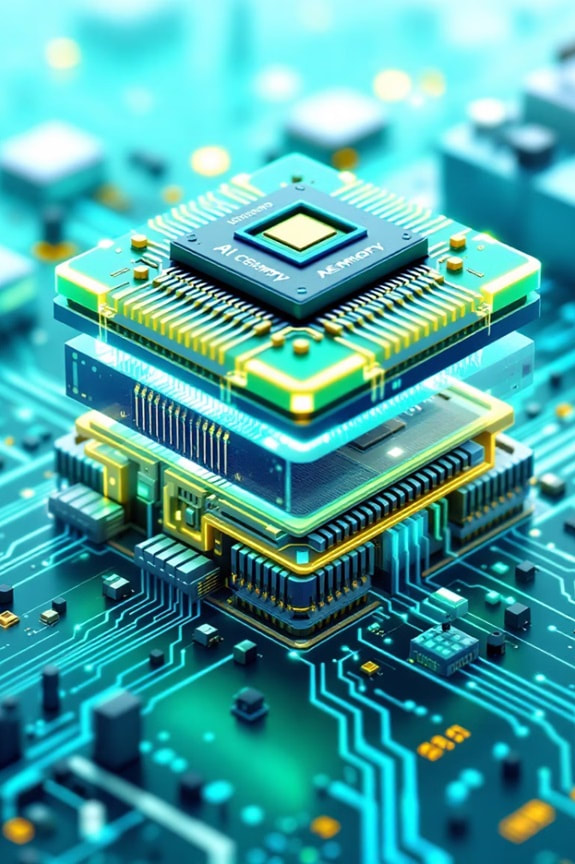

DX-AI

Architecture: High-Band Width (HBM) Potential

Architecture: High-Band Width (HBM) Potential

|

up to 500x

up to 1,000 TB/s Band Width Increase Compared to GPU-HBM4: 2TB/s |

eDX-MRAM: Embedded Memory for AI Chips

|

Embedded Solution

eDX-MRAM provides on-chip memory integration for AI processors. It eliminates the need for separate memory chips. This tight integration reduces latency and power consumption while increasing performance. |

DX-AI Architecture

When integrated with AI compute cores, the architecture is called DX-AI. This allows for revolutionary compute efficiencies. Unlike DRAM, DX-MRAM can be directly integrated with processing elements. |

DX-AI: Revolutionizing AI Chip Architecture

Overcoming HBM Limitations

Vertical Die Structure HBM relies on stacked dies with through-silicon vias. This limits potential I/O scaling between memory and processor. I/O Constraints Current HBM designs max out at 1024-2048 I/O connections. This creates a performance ceiling that's difficult to overcome. eDX-MRAM Solution By enabling direct integration with compute logic, eDX-MRAM enables up to a thousand times more parallel connections than HBM, using metal lines instead of TSVs. This significantly boosts memory bandwidth, as it is directly proportional to the number of I/Os. |